# 24V, 2µA IQ, High PSRR, 500mA Low-Dropout LDO

## **Description**

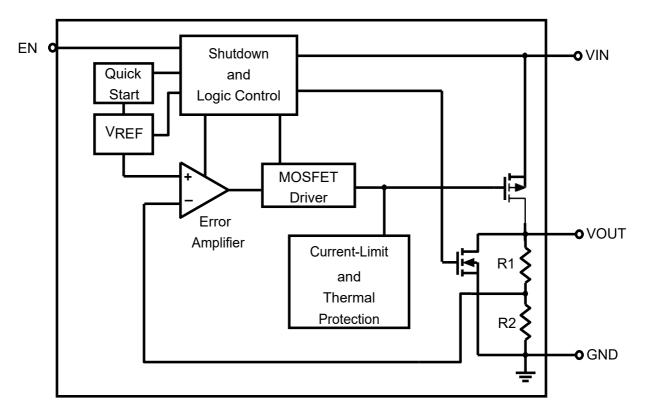

The XR75XX series are high accuracy, CMOS LDO Voltage Regulators, offering Low Power Consumption, high ripple rejection ratio and low dropout. Internally. The XR75XX includes a reference voltage source, error amplifiers, driver transistors, current limiters and phase compensators. The XR75XX 's current limiters' foldback circuit also operates as a short protect for the output current limiter and the output pin.

The XR75XX series is also fully compatible with low ESR ceramic capacitors, reducing cost and improving output stability. This high level of output stability is maintained even during frequent load fluctuations, due to the excellent transient response performance and high PSRR achieved across a broad range of frequencies. The CE function allows the output of regulator to be turned off, resulting in greatly reduced power consumption, ideal for powering the battery equipment to a longer service life.

#### **Features**

- > Low Power Consumption: 2 μA (Typ)

- Maximum Output Current: 500mA

- ► Low Dropout Voltage: 150mV@100mA (Vout=3.3V)

- Operating Voltage Range: 2.5V ~ 24V

- Output Voltage Accurate: ± 1%

- ➤ High PSRR: 70dB @1kHz

- Good Transient Response

- Integrated Short-Circuit Protection

- Over-Temperature Protection

- Output Current Limit

- ➤ Low Temperature Coefficient

- Stable with Ceramic Capacitor

- ➤ RoHS Compliant and Lead (Pb) Free

- ➤ -40°C to +85°C Operating Temperature Range

- Fixed Output Voltage Versions: 1.8, 2.5, 2.8, 3.0, 3.3, 3.6, 4.0, 4.2, 4.4 and 5.0 V

- Available in Green SOT23-3, SOT23-5, SOT89-3, SOT89-5, DFN2x2-6L Packages

# **Applications**

- Portable, Battery Powered Equipment

- Smoke detector and sensor

- Audio/Video Equipmen

- Weighting Scales

- Home Automation

- Electronic fingerprint lock

# **Application Circuits**

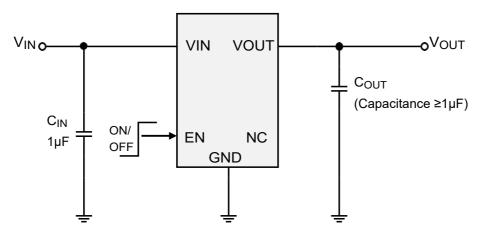

Figure 1. XR75XX Typical Application Circuit

www.szxunrui.cn

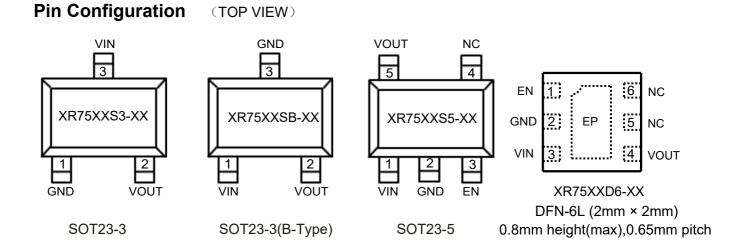

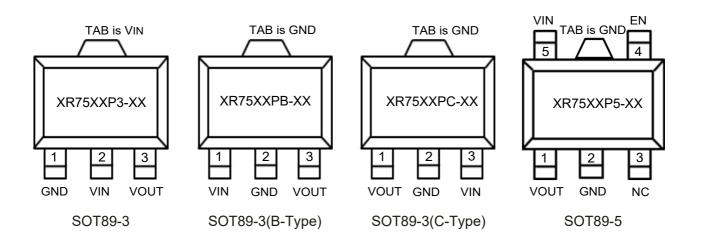

# **Pin Description**

| Pin No. |                                                                                                          |         |    |         |         |          |                       |              |                      |  |

|---------|----------------------------------------------------------------------------------------------------------|---------|----|---------|---------|----------|-----------------------|--------------|----------------------|--|

| SOT23-3 |                                                                                                          | SOT89-3 |    | SOT23-5 | SOT89-5 | DFN2X2-6 | Pin Name              | Pin Function |                      |  |

| S3      | SB                                                                                                       | P3      | РВ | PC      | S5      | P5       | D6                    |              |                      |  |

| 1       | 3                                                                                                        | 1       | 2  | 2       | 2       | 2        | 2                     | GND          | Ground               |  |

| 3       | 1                                                                                                        | 2       | 1  | 3       | 1       | 5        | 3                     | VIN          | Power Input          |  |

| 2       | 2                                                                                                        | 3       | 3  | 1       | 5       | 1        | 4                     | VOUT         | Output Voltage       |  |

|         |                                                                                                          |         |    |         | 3       | 4        | 1                     | EN           | Enable Control Input |  |

|         |                                                                                                          |         |    |         | 4       | 3        | 5、6                   | NC           | No Connect           |  |

| EP /    | EP / TAB In PCB layout, prefer to use large copper area to cover this pad for better thermal dissipation |         |    |         |         |          | r thermal dissipation |              |                      |  |

# **Order Information**

XR75XX ① ②-③ ④

|   | Designator | Symbol                 | Description                                                 |

|---|------------|------------------------|-------------------------------------------------------------|

|   | 12         | S3 , S5 , D6 , P3 , P5 | SOT23-3L , SOT23-5L , DFN6L , SOT89-3L , SOT89-5L           |

| ſ | 34         | Integer e.g 1.8=18     | Output Voltage 1.8,2.5,2.8,3.0,3.3,3.6,4.0,4.2,4.4 and 5.0V |

| Part NO.    | Description                                                | Package   | T/R Qty   |  |

|-------------|------------------------------------------------------------|-----------|-----------|--|

| XR75XXS3-XX |                                                            | SOT23-3L  | 3,000 PCS |  |

| XR75XXS5-XX | XR75XX<br>24V ,2μA IQ ,High PSRR ,500mA<br>Low-Dropout LDO | SOT23-5L  | 3,000 PCS |  |

| XR75XXD6-XX |                                                            | DFN2X2-6L | 5,000 PCS |  |

| XR75XXP3-XX |                                                            | SOT89-3L  | 1,000 PCS |  |

| XR75XXP5-XX |                                                            | SOT89-5L  | 1,000 PCS |  |

# **Marking Information**

For marking information, contact our sales representative directly

All AISIS parts are Pb-Free and adhere to the RoHS directive.

# **Absolute Maximum Ratings**

|                        | Item               | Symbol           | Rating             | Unit   |  |

|------------------------|--------------------|------------------|--------------------|--------|--|

| Supply Input Voltage   |                    | VIN              | -0.3 ~ 24          | V      |  |

| EN to GND              |                    | VEN              | -0.3 ~ 24          | V      |  |

| Regulated Output Volta | ige                | Vout             | -0.3 ~ 6.0         | V      |  |

| Output Current         |                    | Iout             | Internally limited | mA     |  |

|                        | SOT23-3L           |                  | 450                |        |  |

|                        | SOT23-5L           |                  | 500                |        |  |

| Power Dissipation      | SOT89-3L           | ]                | 700                | m-\A/  |  |

| $P_D$ @ $T_A$ =+25°C   | SOT89-3L(B/C-Type) | - P <sub>D</sub> | 950                | mW     |  |

|                        | SOT89-5L           |                  | 1000               |        |  |

|                        | DFN2X2-6L          |                  | 500                |        |  |

|                        | SOT23-3L           |                  | 275                |        |  |

|                        | SOT23-5L           |                  | 250                |        |  |

| Thermal Resistance     | SOT89-3L           | J                | 180                | °C /// |  |

| (Junction to air)      | SOT89-3L(B/C-Type) | θJΑ              | 130                | °C /W  |  |

|                        | SOT89-5L           |                  | 125                |        |  |

|                        | DFN2X2-6L          |                  | 250                |        |  |

| Human Body Model (     | HBM)               | ±4000            |                    | V      |  |

| Charged Device Mode    | (CDM)              | ±2000            |                    | V      |  |

| Machine Mode (MM)      |                    | 200              |                    | V      |  |

| Storage Temperature F  | Range              | Tstg             | -65 ~ +150         | °C     |  |

| Operating Junction Ter | nperature          | TJ               | +150               | °C     |  |

| Lead Temperature (Sol  | dering 10s)        | TLEAD            | +260               | °C     |  |

#### Note:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended period may affect device reliability.

- 2. Ratings apply to ambient temperature at +25°C

- 3. The package thermal impedance is calculated in accordance to JESD 51-7.

# **Recommended Operating Conditions**

| Item                          | Min | Max | Unit |

|-------------------------------|-----|-----|------|

| Operating Ambient Temperature | -40 | +85 | °C   |

| Input Voltage                 | 2.5 | 12  | V    |

| Output Voltage                | 1.8 | 5.0 | V    |

### **Electronic Characteristics**

Test Conditions: VIN = VOUT +1V,CIN=COUT=1uF,TA=25°C,unless otherwise specifi

| Parameter                      | meter Symbol Test Conditions                               |                                       | ditions                                    | Min            | Тур  | Max            | Unit  |

|--------------------------------|------------------------------------------------------------|---------------------------------------|--------------------------------------------|----------------|------|----------------|-------|

| Input Voltage                  | Vin                                                        |                                       |                                            | 2.5            |      | 24             | V     |

| Quiescent Current              | IQ                                                         | VIN=12V, ILOAD                        | =0mA                                       |                | 2    |                | μA    |

| Shutdown Current               | ISHDN                                                      | EN=0 V, Vout =                        | :0 V                                       |                | 0    | 0.2            | μA    |

| Output Voltage                 | Vout                                                       | VIN =12V, ILOAD                       | =1mA                                       | Vout x<br>0.99 |      | Vout x<br>1.01 | V     |

| Output Current                 | lout                                                       | VIN = VOUT +1V                        |                                            | 500            |      | ——             | mA    |

| Drangut Valtage                |                                                            | ILOAD =100mA                          |                                            | ——             | 150  |                |       |

| Dropout Voltage<br>Vo∪⊤ =3.3V  | VDROP                                                      | ILOAD =300mA                          |                                            | ——             | 400  |                | mV    |

| V001 =3.3V                     |                                                            | ILOAD =500mA                          |                                            | ——             | 700  |                | 1     |

| Line Regulation                | ∆ VLINE                                                    | ILOAD =10mA<br>VOUT +1.0V ≦ VIN ≦ 20V |                                            |                | 0.05 |                | % / V |

| Load Regulation                | Load Regulation Δ VLOAD VIN = VOUT +1V 1mA ≦ ILOAD ≦ 100mA |                                       |                                            |                | 5    | 20             | mV    |

| EN Thursday Nobel and          | VCEH                                                       | CE"High"Voltage                       |                                            | 1.5            |      |                | V     |

| EN Threshold Voltage           | VCEL                                                       | CE"Low"Voltage                        |                                            |                |      | 0.4            | V     |

| EN PIN Current                 | len                                                        |                                       |                                            |                | 0.1  |                | μA    |

| Current Limit                  | ILIMIT                                                     |                                       |                                            |                | ——   | 750            | mA    |

| Short Current                  | ISHORT                                                     | Vout = GND                            |                                            |                | 100  |                | mA    |

| Output Noise Voltage           | Output Noise Voltage Von                                   |                                       | COUT =1uF, ILOAD =10mA<br>BW = 10Hz~100kHz |                | 45   |                | μVrms |

| Davis Comple                   | ower Supply PSRR                                           | VIN = 4.3V                            | f=100Hz                                    |                | 85   |                | dB    |

| Rejection Rate                 |                                                            | Vout =3.3V                            | f=1KHz                                     | ——             | 70   |                | dB    |

| Rejection Rate                 |                                                            | ILOAD =10mA                           | f=10KHz                                    |                | 50   |                | dB    |

| Thermal Shutdown Temperature   | $T_{SHDN}$                                                 |                                       |                                            |                | 160  |                | °C    |

| Thermal Shutdown<br>Hysteresis | Ι ΛΤ <sub>εμρ</sub> Ι ——                                   |                                       | _                                          | ——             | 20   |                | °C    |

Note: All limits specified at room temperature (TA = 25°C) unless otherwise specified. All room temperature limits are 100% production tested. All limits at temperature extremes are ensured through correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

# **Functional Block Diagram**

Figure 2. XR75XX Block Diagram

## **Application Guideline**

#### ■ Input Capacitor

$A \geqslant 1 \mu F$  ceramic capacitor is recommended to connect between VIN and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both VIN and GND.

#### Output Capacitor

An output capacitor is required for the stability of the LDO. The recommended output capacitance is ≥1µF, ceramic capacitor is recommended, and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to VOUT and GND pins.

#### ■ Dropout Voltage

The dropout voltage refers to the voltage difference between the VIN and VOUT pins while operating at specific output current. The dropout voltage  $V_{DROP}$  also can be expressed as the voltage drop on the pass-FET at specific output current ( $I_{RATED}$ ) while the pass-FET is fully operating at ohmic region and the pass-FET can be characterized asan resistance RDS(ON). Thus the dropout voltage can be defined as ( $V_{DROP} = V_{IN} - V_{OUT} = R_{DS(ON)} \times I_{RATED}$ ). Fornormal operation, the suggested LDO operating range is ( $V_{IN} > V_{OUT} + V_{DROP}$ ) for good transient response and PSRR ability. Vice versa, while operating at the ohmic region will degrade the performance severely.

#### ■ Thermal Application

For continuous operation, do not exceed the absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated as below:

T<sub>A</sub>=25°C, AISIS DEMO PCB

The max  $P_D = (T_j - T_A) / \theta_{JA}$ .

Power dissipation  $(P_D)$  is equal to the product of the output current and the voltage drop across the output pass element, as shown in the equation below:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$$

#### ■ Layout Consideration

By placing input and output capacitors on the same side of the PCB as the LDO, and placing them as close as is practical to the package can achieve the best performance. The ground connections for input and output capacitors must be back to the XR75XX ground pin using as wide and as short of a copper trace as is practical. Connections using long trace lengths, narrow trace widths, and/or connections through via must be avoided. These add parasitic inductances and resistance that results in worse performance especially during transient conditions.

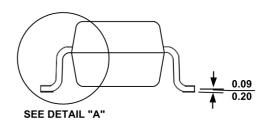

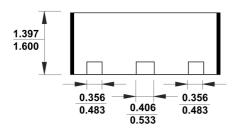

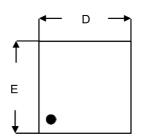

#### **PACKAGE OUTLINE DRAWING FOR SOT23-3**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

SIDE VIEW

**DETAIL "A"**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING IS NOT TO SCALE.

- 6) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

- 7) DRAWING CONFORMS TO JEDEC TO-236, VARIATION AB.

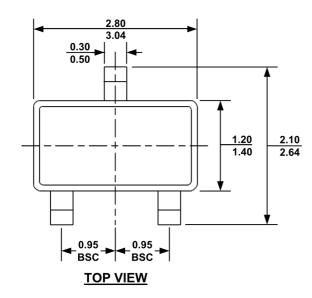

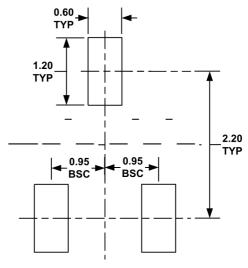

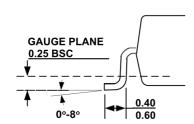

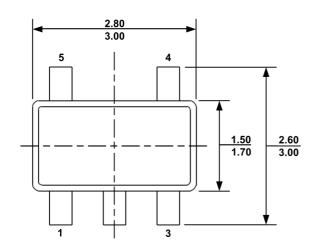

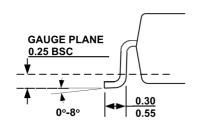

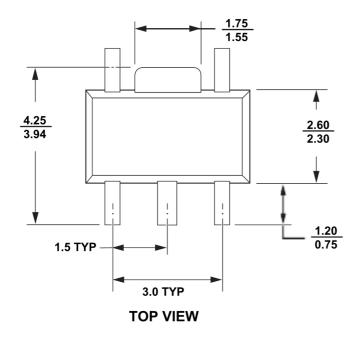

## **PACKAGE OUTLINE DRAWING FOR SOT23-5**

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING IS NOT TO SCALE.

- 6) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

- 7) DRAWING CONFORMS TO JEDEC TO-236, VARIATION AB.

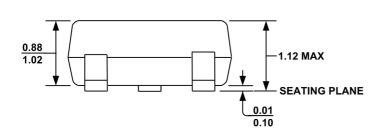

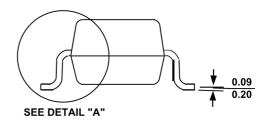

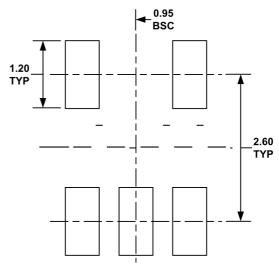

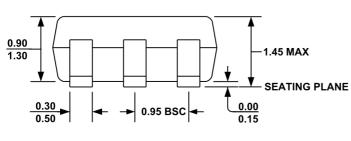

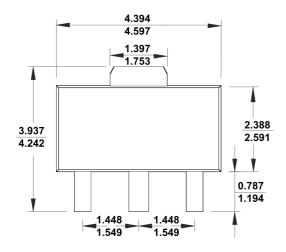

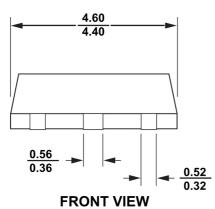

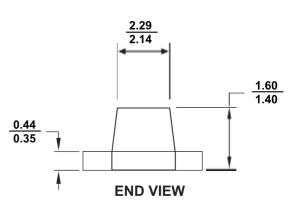

## **PACKAGE OUTLINE DRAWING FOR SOT89-3**

**TOP VIEW**

**SIDE VIEW**

**FRONT VIEW**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING IS NOT TO SCALE.

- 6) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

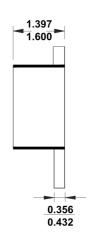

## **PACKAGE OUTLINE DRAWING FOR SOT89-5**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING IS NOT TO SCALE.

- 6) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

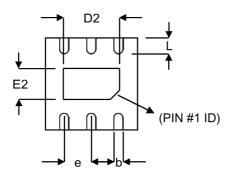

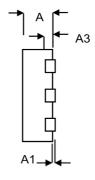

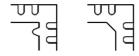

## PACKAGE OUTLINE DRAWING FOR DFN2x2-6L

#### **TOP VIEW**

#### **BOTTOM VIEW**

#### **SIDE VIEW**

| DFN2020-6L           |           |       |  |  |  |  |

|----------------------|-----------|-------|--|--|--|--|

| Dim                  | Min       | Max   |  |  |  |  |

| Α                    | 0.500     | 0.600 |  |  |  |  |

| A1                   | 0.000     | 0.050 |  |  |  |  |

| A3                   | REF       |       |  |  |  |  |

| b                    | 0.250     | 0.35  |  |  |  |  |

| D                    | 1.900     | 0.210 |  |  |  |  |

| D2                   | 1.550     | 1.750 |  |  |  |  |

| Е                    | 1.900     | 0.210 |  |  |  |  |

| E2                   | 0.086     | 1.060 |  |  |  |  |

| е                    | 0.650 BSC |       |  |  |  |  |

| L                    | 0.224     | 0.376 |  |  |  |  |

| All Dimensions in mm |           |       |  |  |  |  |

#### **DETAILA**

PIN #1 ID and Tie Bar Mark Options Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING IS NOT TO SCALE.

- 6) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)